Категория: Руководства

Подробности Автор: EngineerDeveloper®

Система цифрового моделирования проектов на основе VHDL, Verilog и «смешанных» описаний с встроенными функциями анализа производительности, индикации «активности» кода (code coverage), компаратора временных диаграмм и визуализатора Enhanced Dataflow Window. Основные функциональные возможности: высокая скорость моделирования для RTL и Gate проектов; единое моделирующее ядро и оптимизированной архитектуры Native Compiled; интерактивная отладка и анализ с помощью модуля Debug Detective; интегрированный анализ Code Coverage; оптимизация скорости моделирования с помощью анализатора производительности Performance Analyzer; исчерпывающая трассировка сигналов Signal Spy; встроенный отладчик С; поддержка интерфейсов С и Tcl/Tk; поддержка ОС Unix/Windows/Linux.

Вот такие достаточно широкие возможности заложили в этот среду моделирования разработчики. Но в нашем случае все немного проще и задача заключается в том, чтобы промоделировать написанный код. Я пишу на Verilog, поэтому и примеры будут с участием именно этого языка.

Но трудность, как правило, начинающего разработчика заключается не в языке, а в том как бы Modelsim заставить работать совместно с САПРом ISE от ф. Xilinx. И тут многие мне напомнят о том, что у ISE есть родной интегрированный симулятор iSim. Тут я спорить не буду и соглашусь. Но iSim в большинстве случаев пользуют при отладке чего-то не очень сложного, хотя я знаю случаи когда люди принципиально пользовались iSim при моделировании достаточно сложных проектов. Это личное дело каждого. Проводить сравнение этих двух симуляторов я не буду по причине бессмысленности. Отмечу лишь следующее, что разработчики Xilinx ISE заложили возможность пользоваться средой Modelsim из ISE (запускать).

На видео я покажу, как настроить ISE для работы с ModelSim.

Для начала необходимо установить ModelSim. На первом видео приведен порядок установки.

Далее необходимо внести некоторые изменения в настройки ISE и сгенерировать библиотеки в ISE для ModelSim. Этому я посветил свой второй видеоролик.

Первым делом нужно удостовериться, что в среде разработки Quartus II указан путь к инструменту ModelSim. Для этого открываем меню Tools -> Options. В опциях переходим к пункту General -> EDA Tool options. Находим поле ModelSim-Altera и впечатываем в него C:\altera\13.0sp1\modelsim_ase\win32aloem или, нажав на кнопку с тремя точками, ищем эту директорию у себя на компьютере. Естественно, для версии Quartus, отличной от моей, у вас будет свой путь к директории "win32aloem".

У вас есть проект для ПЛИС в Quartus II. Как писать тесты, или тестбенчи (testbench) - это тема для отдельной статьи. Сейчас же предположим, что ваш тестбенч уже написан. Теперь нужно указать среде разработки, какой тест вы хотите использовать при симулировании. Для этого открываем настройки через меню Assignements -> Settings. В открывшемся окне, в разделе EDA Tool Settings -> Simulation. нажимаем кнопку Test Benches. Здесь, кстати, можно задать несколько тестов и при компиляции проекта переключаться на нужный.

Открылось окно редактирования тестов Test Benches. Пока что мы не создали ни одного тестбенча, поэтому список пустой. Нажимаем кнопку New. В открывшемся окне New Test Bench Settings нужно задать настройки теста.

Слева от поля File name нажимаем на кнопку с тремя точками. Выбираем файл с кодом тестбенча и нажимаем Open. Теперь нажимаем кнопку Add. Тест появился в списке тестов.

После этого в поле Top level module in test bench зададим название модуля верхнего уровня, который определён в вашем тестбенче. Имя в поле Test bench name можете вписать любое, по умолчанию оно будет автоматически создано таким же, как имя модуля.

Всё, мы задали основные настройки теста. Нажимаем два раза ОК. Теперь наш тест появился в выпадающем списке тестбенчей. Ещё раз нажимаем ОК .

Если вы ещё не сделали синтез проекта, то пора это сделать. Выберите в меню Processing -> Start -> Start Analysis & Synthesis. или нажмите комбинацию клавиш Ctrl+K. или просто кликните соответствующую иконку в верхней панели.

Можно запускать симулирование. Выбираем в меню Tools -> Run Simulation Tool -> RTL Simulation (1) или нажимаем иконку RTL Simulation в верхней панели (2).

Запустится инструмент ModelSim. который выполнит все инструкции, прописанные в вашем тестбенче, и остановится (если вы специально указали это директивой $stop в коде теста). На экране появятся диаграммы уровней входных и выходных сигналов ПЛИС, которые вы описали в вашем проекте.

В окне Transcript (меню View -> Transcript) отображаются все операции, которые производит ModelSim. Если симулирование завершилось с ошибкой, вы увидите сообщение об этом. Причём будет указан даже номер строки в коде вашего теста, который вызвал ошибку ModelSim. Эта информация очень полезна для локализации и устранения ошибок.

Как провести моделирование с помощью ModelSim - Altera

Не получили ответ на свой вопрос?

Спросите нашего эксперта:

Все эксперты в этой области

Добавить комментарий к статье

Последние вопросы на форуме эксперта

Спасибо за информацию. А возможно ли где-то ещё найти дистрибутив Quartus II Web Edition версии 3.0? На официальном сайте лицензию выдали без вопросов, а вот загрузка исполняемого файла установки самого.

Новые советы от КакПросто

Что выбрать: традиционный нетбук или планшет с клавиатурой?

Рынок мобильной техники предлагает все больше интересных гаджетов, которые можно брать с собой для работы.

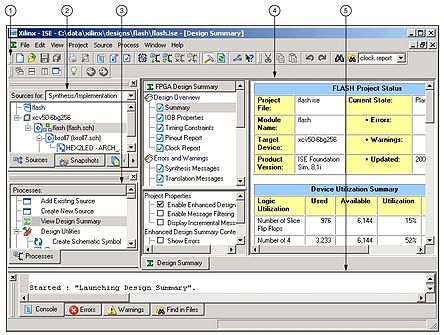

Статья предназначена для людей знакомых с ModelSim и начинающим своё знакомство с Xilinx ISE. Не желаете разбираться во встроенном симуляторе Xilinx ISE? Любите и хотите продолжать работать в ModelSim? В этом вам поможет эта небольшая статья.

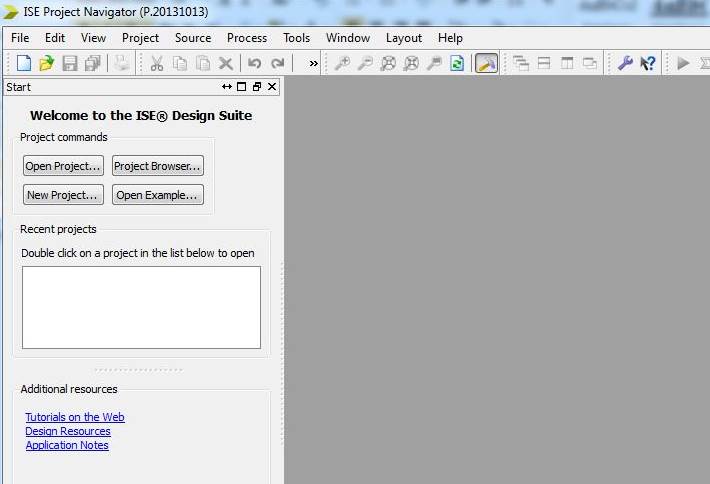

У вас установлен нужный софт(ну или будет установлен в ближайшее время). У меня стоит 9-я версия ISE и ModelSim версии 6.5.Сперва укажем в настройках ISE путь к ModelSim. Заходим Edit -> Preferens -> ISE General -> Integrated Tools

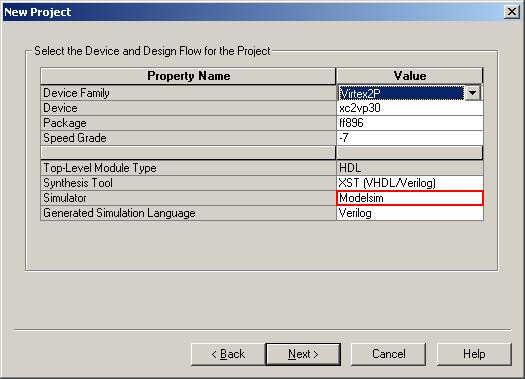

Нажимаем кнопку справа и указываем путь к *exe файлу ModelSim(мой путь выглядит так — C:\modeltech_6.5b\win32\modelsim.exe).Жмем OK. Теперь при создании проекта можно смело выбирать ModelSim в качестве симулятора.

Если у вас уже создан проект и вы хотите переключиться на ModelSim, нужно зайти в настройки проекта и внести соответствующие изменения.

Нажимаем правой кнопкой мышки и выбираем пункт меню Properties.

И выбираем из уже знакомого нам выпадающего меню нужный вариант.

Если при симуляции ModelSim ругается на отсутствие библиотек их необходимо подключить.Заходим в ModelSim и создаем новую библиотеку File -> New -> Library

В окне Create a New Library выбираем пункт a map to an existing library. Указываем путь к папке с библиотекой и вводим имя библиотеки. Имя папки и имя библиотеки должны совпадать!

Конечный итог должен быть примерно таким:

Жмем OK. Наша библиотека подключена.

Update: 5 библиотек cpld,simprim,unimacro,unisim,xilinxcorelib

Только зарегистрированные и авторизованные пользователи могут оставлять комментарии.

EasyEDA: бесплатный Облачный CAD

Когда угодно. Где угодно! На Linux, Mac, Windows, Android, PC, планшете или смартфоне. Откройте браузер, войдите в систему и продолжайте работать. Можно вести приватную или коллективную разработку, а также расшаривать свои проекты всему миру.

Прямой эфирКалмыков П.В. Взаимодействие simulink и modelsim.

< Документ в стадии редактирования >

В данной работе рассказаны основы установки связи между Simulink и ModelSim. Это позволит моделировать программу написанную на языке VHDL или Verilog, подавая на вход модели синтезируемые в среде Simulink (MatLab) значения.

Замечание

Для соединения Simulink и ModelSim необходимо издание ModelSim SE либо ModelSim PE. Версии ModelSim ХE, ModelSim АЕ и другие не поддерживаются.

Общие указания

Данная работа выполняется на персональном компьютере с операционной системой Windows и установленными программными комплексами Simulink и ModelSim SE/PE.

Для начала работы необходимо создать описание программы на языке VHDL либо Verilog. Если у вас есть уже готовый файл, следующий пункт можно пропустить.

1. Написание основного кода

В данной работе рассмотрен пример написанный на языке VHDL. Дня написания основного кода можно воспользоваться любым редактором. Для примера воспользуемся САПРом фирмы Xilinks. Запускаем Xilinks (WebPack) ISE. Далее File >> New Project. Вводим имя проекта (в данном случае inverter). На следующей странице выбираем тип используемого устройства (в данной работе не существенны эти параметры). Далее. На следующей странице (Create New Source) нажимаем "New Source", из списка выбираем VHDL Module, вводим имя (main). На следующей странице вводим следующие сигналы: clk [in], reset[in], din(7:0)[in], dout(7:0)[out]. Остальные пункты пропускаем.

Пишем исходный код программы:

library IEEE ;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity main is

Port ( clk: in STD_LOGIC ;

reset: in STD_LOGIC ;

din: in STD_LOGIC_VECTOR (7 downto 0) ;

dout: out STD_LOGIC_VECTOR (7 downto 0)) ;

end main;

architecture Behavioral of main is

begin

pr: process (clk)

begin

if rising_edge(clk) then

if reset = '1' then

dout <= "00000000" ;

else

dout <= not din ;

end if ;

end if ;

end process ;

end Behavioral ;

Сохраняем. Данная программа инвертирует входящий 8-биный вектор. При желании можно использовать намного более сложные конструкции.

2. Создание библиотек и компилирование проекта

Теперь необходимо создать библиотеку данного проекта в ModelSim'е. В этой библиотеке будут содержаться результаты компиляции.

Запускаем ModelSim SE/PE. Для начала необходимо указать директорию, в которой находится файл с программным кодом (в данной работе …/Xilinx/Work/inverter). File >> Change Directory. Другой способ выбора директории – это прописать команду в окне Transcript.

cd <путь к папке проекта>

(например: cd D:/Programs/Xilinx/Work/inverter).

<<внимательно отнеситесь к пробелам и русским буквам в пути к папке с проектом>>

Далее в этой же командной строке вводим:

ModelSim> vlib work

ModelSim> vmap work work

Команда vlib создает непосредственно саму библиотеку в которой будут содержаться результаты компиляции. Команда vmap отображает логический уровень программы к физическому каталогу.

В случае если библиотека уже создана ModelSim выдаст сообщение в командной строке:

# ** Warning: (vlib-34) Library already exists at "work".

Далее скомпилируем файл программы:

vcom <file_name>.vhd

ModelSim> vcom main.vhd

3. Создание Simulink модели

Запускаем Simulink. Создаем новую модель File >> New >> Model. Выбираем следующие элементы (Рис 1):

Sources – Sine wave .

Sources – Step .

Commonly Used Block – Data Type Converter .

Sinks – Scope .

Link for ModelSim – HDL Cosimulation .

Два раза щелкнув мышкой на блок HDL Cosimulation изменим его параметры. Для начала необходимо описать входы/выходы на вкладке Ports как показано на рис.2. Выбираем порт, изменяем необходимые данные. Для сохранения изменений необходимо нажать кнопку Update.

На вкладке Clocks необходимо добавить тактовый сигнал (рис.3). Нажимаем кнопку New, вводим параметры, нажимаем кнопку Update.

Вкладку Timescales оставляем без изменений.

На вкладке Connection выбираем Connection method: Socket. Эта опция определяет, что Simulink и ModelSim будут общаться через определяемый порт TCP/IP. Номер порта оставим по умолчанию 4449.

На последней вкладке Tcl измените строчки как показано на рисунке 6.

Pre-simulation commands: echo "Running Simulink Cosimulation block."

Post-simulation commands: echo "done"

Установим параметры других блоков.

Блок Sine Wave:

Sine type: Time-based

Time(t): Use simulation time

Amplitude: 128

Bias: 0

Frequency: 0.02

Phase: 0

Sample time: 10

Блок Data Type Conversion ( соединенный с Sine Wave ):

Блок Data Type Conversion ( соединенный с Step ):

В результате, соединив все блоки между собой получим модель изображенную на рисунке 11.

Так же, необходимо установить настройки моделирования. В окне модели выбираем Simulation >> Configuration Parameters (рис. 12).

Устанавливаем параметры моделирования (рис.13).

Start time: 0

Stop time: 1000

Type: Fixed-Step

Solver: discrete

Periodic sample time constraint: Unconstrained

Fixed-step size: auto

Tasking mode for periodic sample times: auto ( в некоторых случаях необходимо выбрать Single Tasking)

Сохраняем Simulink модель (название не существенно, в данном случае Test, путь так же не существенен, но для удобства лучше использовать папку с проектом).

4. Подключение к ModelSim 'у.

Теперь у нас есть готовый VHDL файл и модель входных сигналов в Simulink'е. Для подключения ModelSim'а к Simulink'у необходимо в командной строке MatLab'а ввести:

Если ранее был указан другой порт, то необходимо ввести именно его.

После загрузки ModelSim 'а необходимо указать директорию, в которой находится Ваш VHDL файл:

File >> Change Directory либо в командной строке cd <путь к папке проекта>

( например. cd D:/Programs/Xilinx/Work/inverter)

5. Симуляция и вывод сигналов

Далее следует ввести в командной строке:

ModelSim> vsimulink work.main

ModelSim запускает vsim симулятор, который моделирует программу на VHDL. Для вывода временных диаграмм сигналов необходимо ввести в командной строке:

VSIM n > add wave -in -label clk clk

- выводит на экран входной сигнал тактовой частоты clk

VSIM n > add wave -in -label reset reset

- выводит на экран входной сигнал сброса reset

VSIM n> add wave -color Yellow -analog-interpolated -height 45 -in -radix decimal -scale 0.1 -label din din

-выводит на экран входной сигнал din (цвет желтый, вид аналоговый (сглаженный), высота 45, входящий, в десятичном виде, шкала 0.1).

VSIM n> add wave -color White -analog-interpolated -height 45 -out -radix decimal -scale 0.1 -label dout dout

-выводит на экран выходной сигнал dout (цвет белый, вид аналоговый (сглаженный), высота 45, входящий, в десятичном виде, шкала 0.1)

Так же добавлять сигналы можно просто перетаскивая названия сигнала из окна Objects в окно Wave. либо нажимая на имя сигнала (в окне Objects ) правой кнопкой мыши Add to Wave >> Selected Signals . Однако, у способа ввода через командную строку есть преимущества, можно заранее указывать параметры (Properties ) выводимого в окне Wave сигнала.

Нажимаем кнопку Start Simulation в модели Simulink' а. Результаты моделирования показаны в окне Wave в ModelSim 'е.

Для более упрощенного ввода параметров моделирования, можно создать выполняемый do -файл . Для этого создайте текстовый файл. Запишите построчно:

vsimulink work. main

add wave -in -label clk clk

add wave -in -label reset reset

add wave -color Yellow -analog-interpolated -height 45 -in -radix decimal -scale 0.1 -label din din

add wave -color White -analog-interpolated -height 45 -out -radix decimal -scale 0.1 -label dout dout

Сохраните файл с расширением *. do (как пример: main. do ). Поместите do -файл в папку проекта VHDL. Теперь вместо пункта 5 пишите в командной строке:

После чего можно запускать симуляцию (Start Simulation) в модели Simulink'а.

И снова здравствуйте, друзья! В этом, шестом по счету видеоуроке на сайте LOGWAYS.RU мы научимся основам работы в HDL-симуляторе ISim, который входит в пакет программ XILINX ISE Webpack 13.2.

Итак, открывает ярлык на рабочем столе Xilinx ISE Design Suite 13.2. В окне Design в панели View ставим метку напротив строки Simulation .

В окне Hierarchy выбираем элемент antitwit_nofix.vhd. В окне Processes выполняем предварительную проверку синтаксиса, выбрав команду BehavioralCheckSyntax. После успешной проверки синтаксиса запускаем команду SimulateBehavioralModel.

Перед нами – основное окно программы ISim. Здесь в окне Objects нам необходимо указать типы входных воздействий (т.е. какими будут наши входные сигналы). Для этого в контекстном меню входного порта INSIG выбираем команду Force Clock. Если у нас период сигнала начинается с единицы, то в поле Leading Edge Value указываем значение ‘1’, а в поле Trailing Edge Value – ‘0’. Если очередной период начинается с нуля, то наоборот.

В полях Starting at Time Offset и Cancel after Time Offset можно указать величину сдвига в начале периода сигнала относительно начала процесса симуляции и соответственно конца периода сигнала. Мы указываем нулевые сдвиги.

В поле Duty Cycle (%) указываем скважность сигнала (а скважность, как известно, это отношение длительности импульса к его периоду). Мы укажем величину 5 %.

И наконец, в поле Period указываем период входного сигнала INSIG. Напоминаю, что сигнал INSIG, это входной сигнал с флуктуациями от дребезга контактов. Эти флуктуации нам и нужно устранить. Укажем период сигнала, равным, например, 1 секунде (1s).

Кстати, в программе ISim все временные величины, если не указана размерность, выражены в пикосекундах. Если мы хотим иную размерность, то так указываем: 10s, 56ms, 3.4us, 467ns.

Точно таким же образом указываем параметры входного сигнала для порта N1kHz. В поле Period, соответственно, указываем величину 1ms.

Далее, необходимо указать время симуляции в поле рядом с кнопкой Run (синий треугольник с песочными часами). Укажем время симуляции 10 секунд (10s). После этого запускаем симуляцию, нажав кнопку Run.

После окончания симуляции возникнет необходимость просмотра всей временной области сигналов, для чего нажимаем кнопку ZoomtoFullView .

Итак, судя по осциллограммам, мы можем видеть, что наш элемент защиты от дребезга работает идеально. Как только появляется фронт входного воздействия на порте INSIG, на выходе OUTSIG возникает импульс с периодом 256 мс. Величина эта постоянная и никакие последующие флуктации на входе INSIG не в состоянии её изменить.

Так же мы можем наблюдать, как изменяются состояния внутренних сигналов и шин элемента защиты от дребезга.

Таким образом, в этом видеоуроке мы научились основам работы со встроенным HDL-симулятором ISim пакета программ XILINX ISE WebPack 13.2. До скорых встреч!

Об авторе adminИнженер. Окончил НГТУ по специальности "Радиосвязь, телевидение и радиовещание". С 2003 г. занимаюсь разработкой электронной начинки различных радиотехнических устройств и приборов.